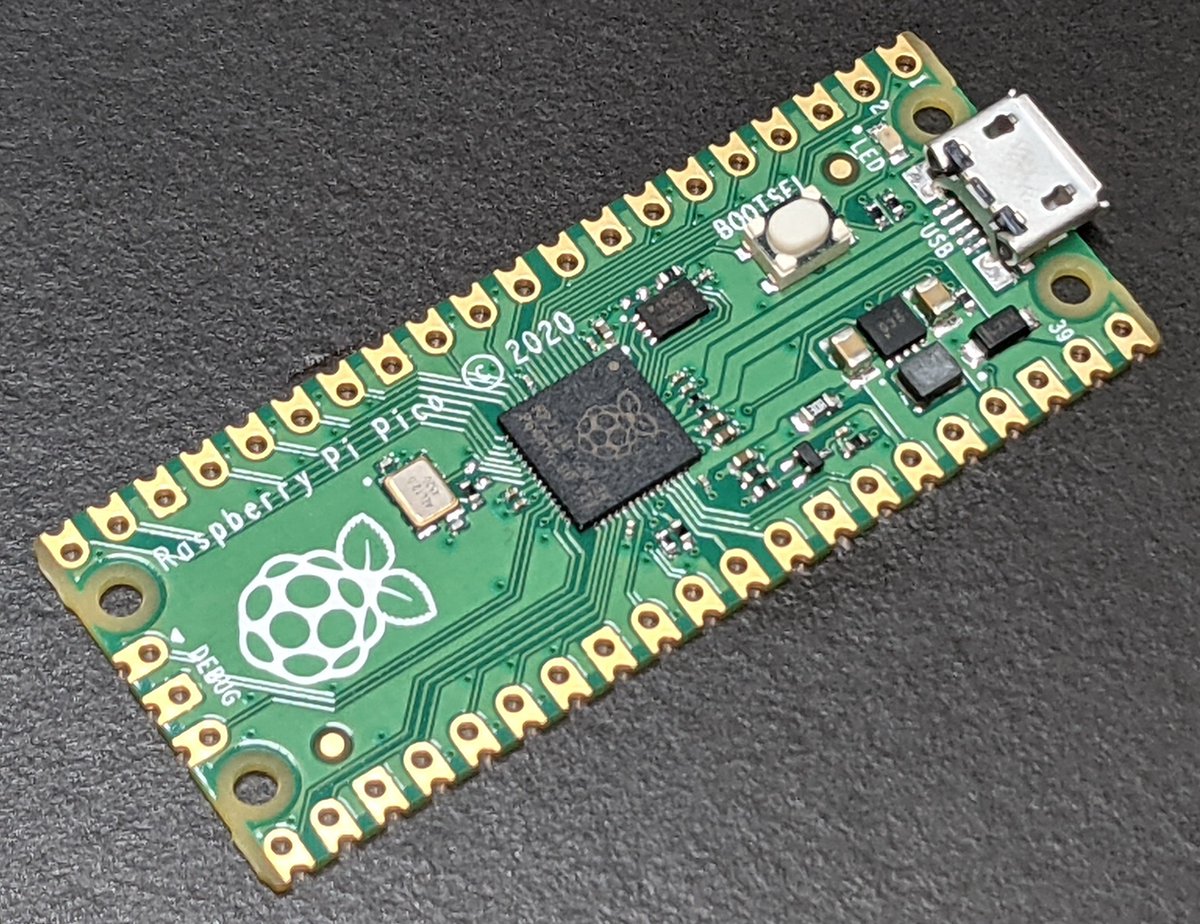

#RaspberryPiPico silicon teardown time!

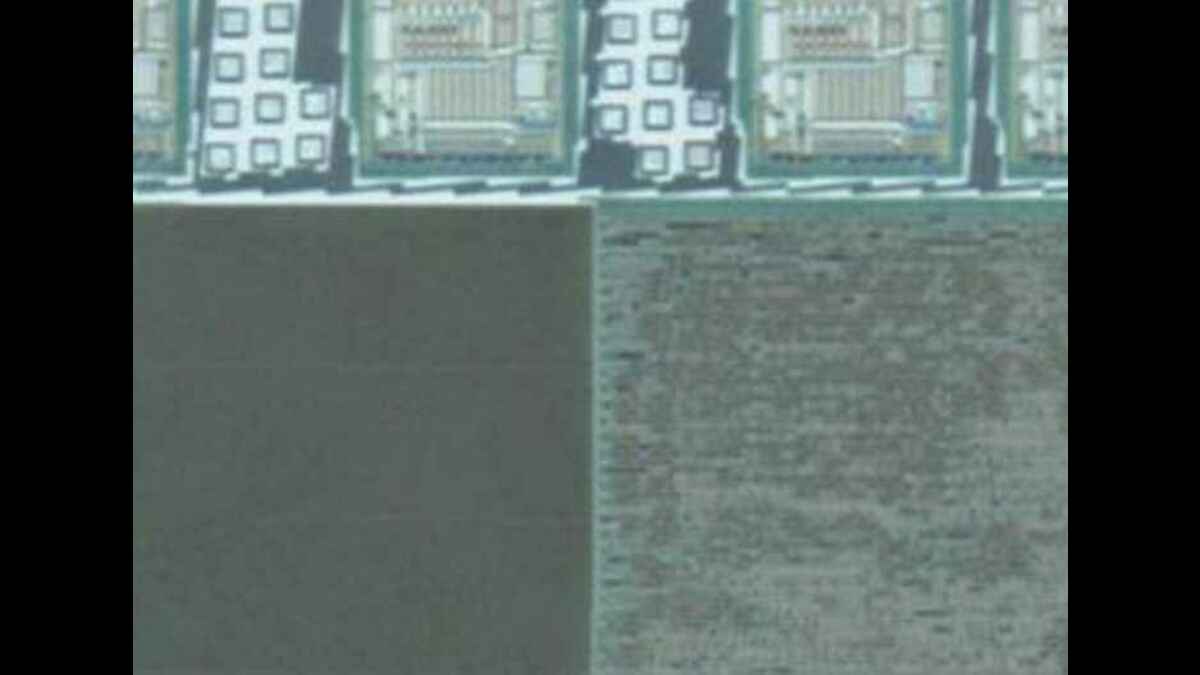

Decapped to show copper bond wires connecting die to package pins. Initially used only nitric acid which destroyed copper bond wires (last image). Fixed by switching to mixed nitric + sulfuric acid

Zoomable top metal die image: siliconpr0n.org/map/raspberry-…

@Raspberry_Pi marking it's turf

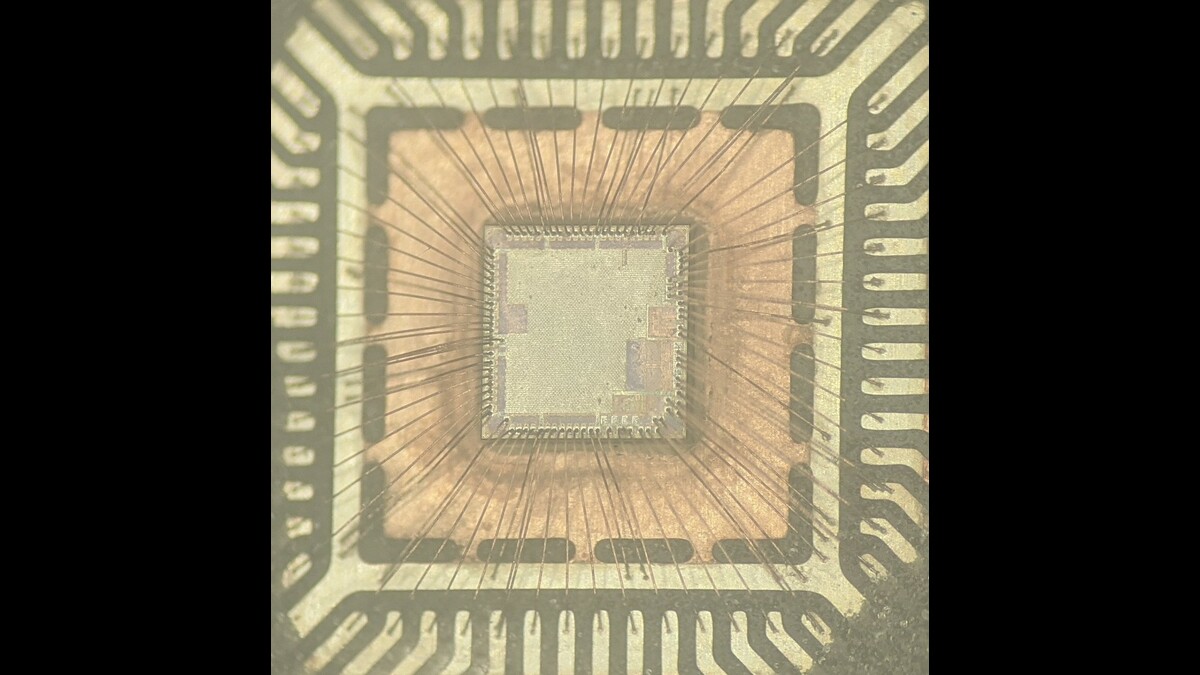

B0 => chip revision. On every layer? A chip I worked on did this and unfortunately when we fixed a bug on a *different* metal layer we didn't want to remake the masks with the text. Thus "B1" chips were mislabeled as B0!

M8 => eight metal layer chip. Higher metal layers are coarser to carry more power and reduce manufacturing costs. You can also see M7 and M6 marked

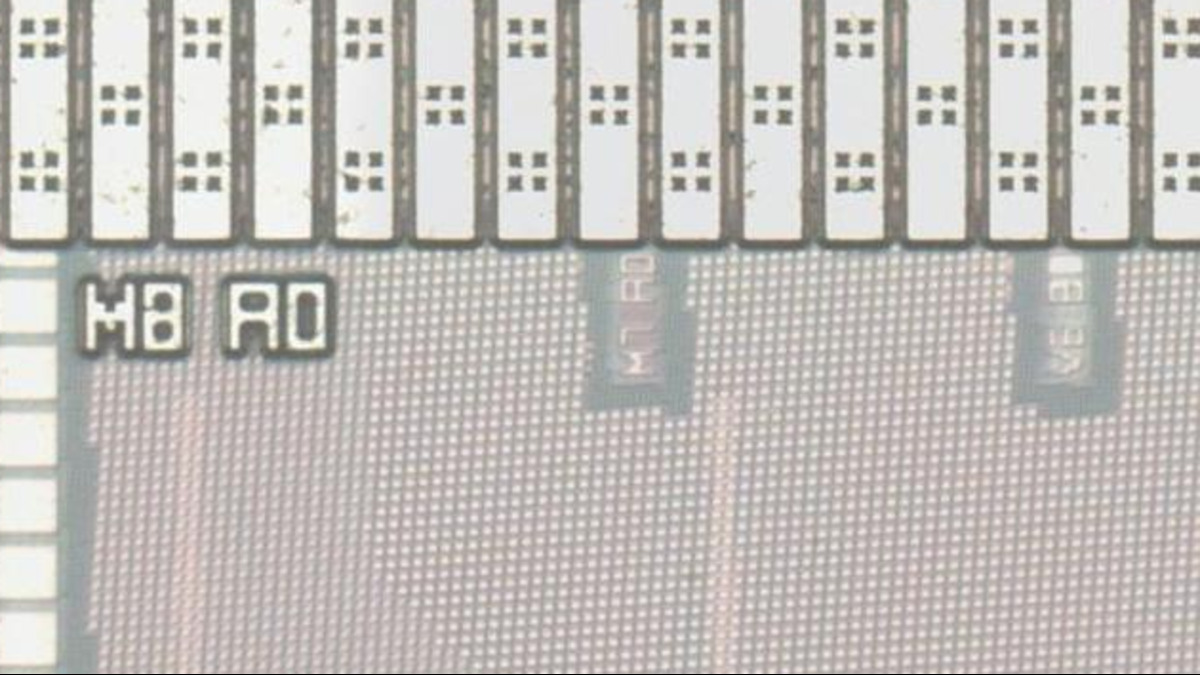

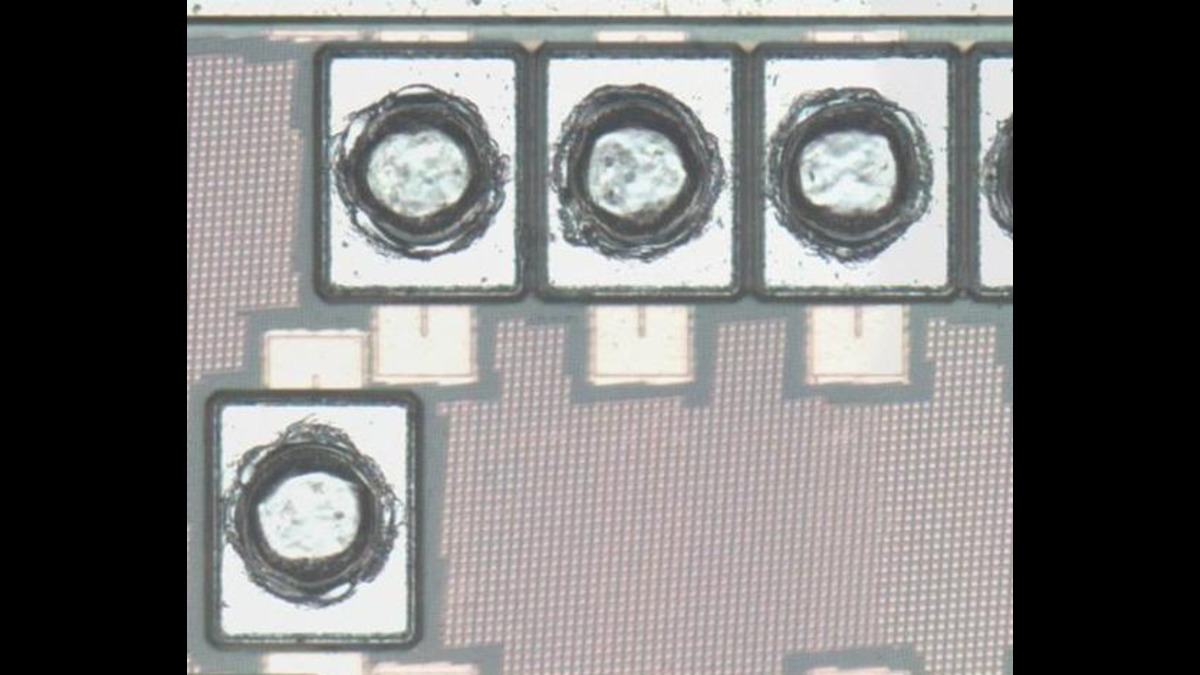

Copper bond wires were eaten by nitric acid leading little dimples where they used to be attached to the bond pads

Time lapse etching chip layers

1) 20x air vs 2) 60x oil objective: 60x has higher resolution but lower depth of field, making the image appear different. Ex: although the lower left splotch is large, it's only visible in the 60x image. I might take SEM images later for better resolution

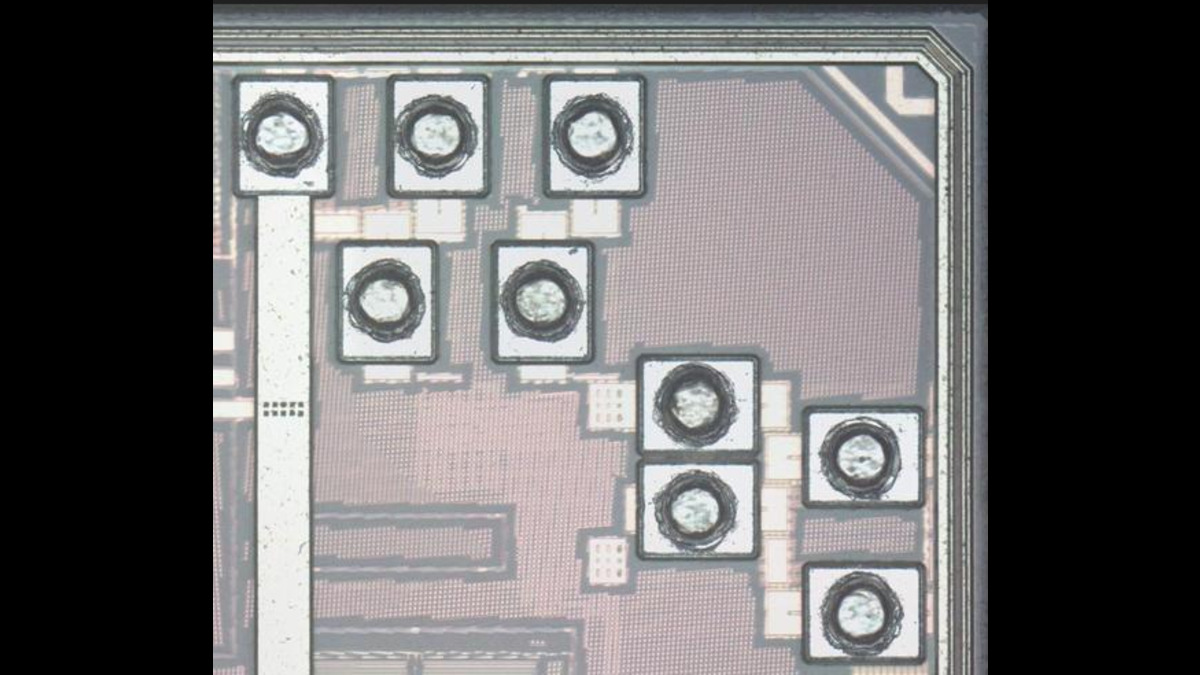

Transistors arranged into standard cells form the majority of the digital logic. This includes both the CPU and the digital portion of most peripherals

A few different I/O showing logic, ESD protection, etc between the top metal and transistor layer. A number of different I/O IP blocks are used. Would be interesting to match them up to the datasheet for analog functionality like ADC, USB, etc

SRAM is scattered throughout the die. By analyzing the memory sizes and comparing to the datasheet it might be possible to guess what some of these are for

CMP fill is added to unused areas to keep polishing more even when preparing for the next layer. As such, it looks like it was omitted on M8 (top metal) but is found on other layers

That's all for now. Hope you enjoyed and let me know if you want more information on something!

• • •

Missing some Tweet in this thread? You can try to

force a refresh